國研院半導體中心旺宏電子合作開發 新型高密度高頻寬3D動態隨機存取記憶體

新網記者麻念台台北特稿

2025/2/25 下午 01:03:03 / 電腦實境

AI人工智慧產品已廣泛使用在各行各業的不同情境,其中負責儲存資料的隨機存取記憶體(Random Access Memory, RAM)元件,在AI晶片中扮演著至關重要的角色。國科會轄下國家實驗研究院台灣半導體研究中心與臺灣記憶體製造大廠旺宏電子公司合作,成功開發出「新型高密度、高頻寬3D動態隨機存取記憶體」(3D DRAM),具有體積小(高密度)、高頻寬、能耗低、耐用度高等優勢,是全世界最早開發出此種新型3D DRAM的團隊之一。

|

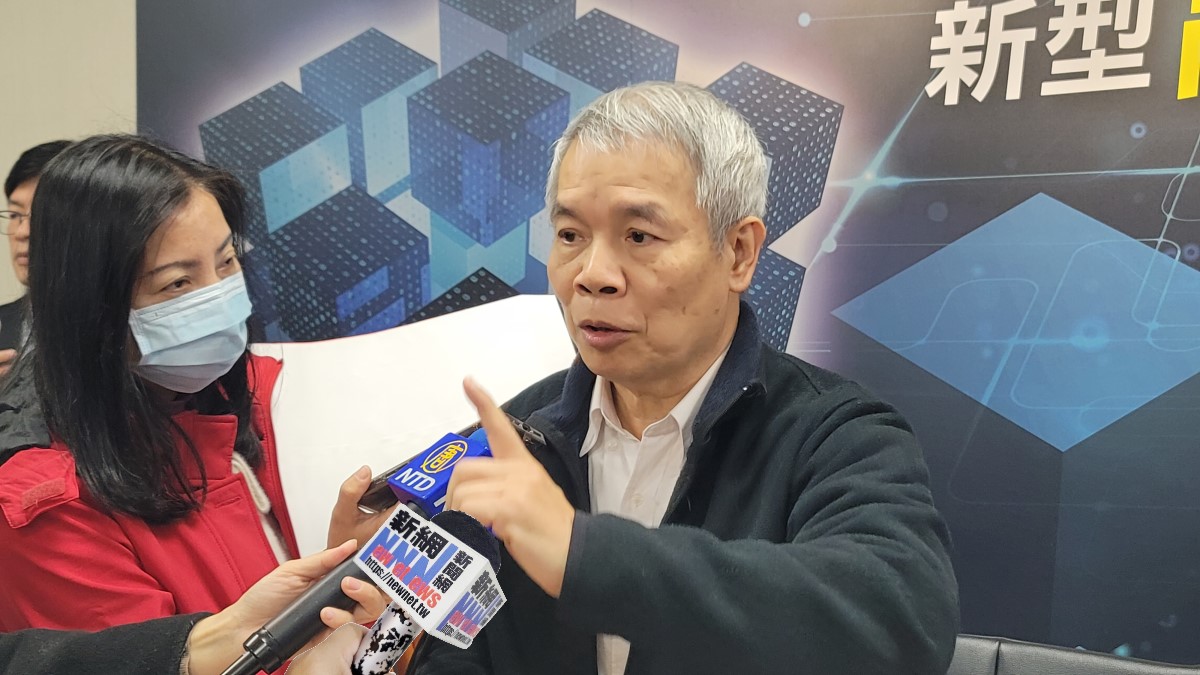

| 國研院半導體中心元件技術組研究元楊智超(左)說明研發新型高密度高頻寬3D動態隨機存取記憶體現況。(歸鴻亭攝影) |

國研院半導體中心元件技術組研究元楊智超表示,該中心透過長期產學合作機制,協助產學研團隊進行前瞻半導體技術開發,與國際發展趨勢接軌,並將合作成果轉化為培育國內碩博士級高階研究人力的服務平台。旺宏電子作為全球的積體電路指標性廠商,亦持續投入產學合作,深耕臺灣半導體人才培育。本次雙方合作,除證明國內研究於相關領域已躋身國際領先團隊外,也期望透過半導體中心世界領先的學研平台與培育人才機制,協助臺灣高階半導體人才與未來主流技術接軌,深化臺灣半導體科技之研發量能。

楊超智指出,記憶體在AI時代越發重要,因為它直接影響到AI晶片處理數據的速度、效率和可靠度,不論是AI訓練、穿戴式裝置、醫療電子、車用電子、智慧家電…等,記憶體都扮演重要角色。傳統2D平面製作的記憶體已達密度上限,為了尋求突破,記憶體廠商紛紛將研發焦點轉向3D堆疊記憶體,就像是把平面停車場改為立體停車塔,如此便能在相同的面積上大幅提升記憶體密度。其中,簡稱DRAM(Dynamic Random-Access Memory)的動態隨機存取記憶體,因為具備讀寫速度快、高耐久和低成本的特點,而成為AI晶片中暫存記憶體的主流。

|

| 國科會轄下國家實驗研究院台灣半導體研究中心與臺灣記憶體製造大廠旺宏電子公司合作,成功開發出「新型高密度、高頻寬3D動態隨機存取記憶體」。(歸鴻亭攝影) |

AI晶片需要進行極大量、極快速的資料運算,在現在的AI晶片整體架構中,是利用半導體封裝技術,將2D平面製作的DRAM層層堆疊及串連在一起,製作高頻寬記憶體HBM(High Bandwidth Memory),然而記憶體的頻寬仍受到此封裝技術上的限制,加上現有的DRAM耗能也高,增加了AI晶片的總耗電量。因此,如何製造出更高頻寬(傳輸訊號更快)、更高密度(更大容量)且更低耗能的HBM,成為目前全世界各研發單位及記憶體大廠的主軸研發方向。

HBM中DRAM的基本單位是一個電晶體加一個電容所組成,以電晶體作為開關,對電容進行充電或放電,來記錄1或0。國研院半導體中心與旺宏電子合作開發的3D DRAM,不使用傳統記憶體中體積較大的電容,而以兩顆氧化銦鎵鋅(Indium Gallium Zinc Oxide, IGZO)電晶體串聯而成,可將0與1的訊號儲存在兩顆電晶體之間。這種無電容的新型結構設計,讓記憶體尺寸變得更小,因而在進行3D堆疊時能更緊密,也消除了電容造成讀寫速度慢及耗能高的缺點。

|

| 旺宏電子前瞻技術實驗室資深處長謝光宇說明要實現HBM記憶體的3D堆疊,最重要的是要避免加熱製作上層記憶體時,「熱」損壞下層已經製作好的半導體元件。(歸鴻亭攝影) |

此外,由於使用新材料氧化銦鎵鋅製作電晶體,這是一種寬能隙半導體材料,可降低儲存訊號隨時間而流失的機率,進而延長記憶體的資料保存時間。相較於傳統的DRAM,保存時間可延長達數千至數萬倍以上,這代表耗電儲存與讀取資料的間隔時間也可以大幅拉長,因而大幅降低能耗。此外,這種新型記憶體的高耐久度亦得到實際驗證,是應用在AI人工智慧晶片的HBM記憶體首選。

要實現HBM記憶體的3D堆疊,最重要的是要避免加熱製作上層記憶體時,「熱」損壞下層已經製作好的半導體元件,尤其在縮小記憶體尺寸後,上下層之間的距離更近,更容易受到影響。國研院半導體中心的「積層型3D晶片製程服務平台」,歷年來已開發出多項低溫製造技術,近5年(2020年至今)協助台灣學研界發表過高達83篇以上的IEDM、VLSI等國際指標性會議論文。此低溫製造技術極具應用潛力,能讓下層元件保持在低溫環境中,可應用於層層堆疊的HBM記憶體製造。

|

| 國研院半導體中心將持續投入前瞻半導體製程技術的研發。(歸鴻亭攝影) |

另一項技術重點是透過旺宏電子的Bit-Cost Scalable專利製程技術,旺宏電子前瞻技術實驗室資深處長謝光宇說明,先將許多層記憶體的電流通道做垂直堆疊,再利用一次性的蝕刻,將記憶體單元陣列製作出來,大幅減少了3D堆疊記憶體的製程步驟,能節省製作時間、降低成本。最後雙方合作成功開發出「新型高密度、高頻寬3D動態隨機存取記憶體」,可用於AI晶片中HBM記憶體。目前全世界僅有數個頂尖研究團隊提出此種3D DRAM的雛形及結構,均仍在實驗階段,尚未進入量產,未來半導體中心與旺宏電子合作開發的新型3D DRAM若順利導入量產,將能在全世界建立起領先的地位。

為了迎接未來AI人工智慧科技變革的契機與挑戰,配合國家的「晶片驅動臺灣產業創新方案」,國研院半導體中心將持續投入前瞻半導體製程技術的研發,並透過長年建立的產學合作機制及訓練服務經驗,接軌業界實務研發需求,建立埃米(angstorm)世代先進半導體元件、材料、電路技術研發平台,培育高階研究人力,讓國內半導體設計與製造人才養成能更進一步貼近產業發展需求。